## **Request for Information (RFI) Summary: SDO Responses & Analysis**

Christine Bernat, Associate Director, Standards Facilitation, ANSI

DoD microelectronics kick-off 27 July 2022

# Department of Defense RFI 2020

## Objectives

- Identify Standards Development Organizations (SDOs) activities;

- Gain understanding about procedures, policies, participation, and fees;

- Learn history and engagement with federal & other government agencies;

- Determine interest for supporting future ME standards development.

## Respondents

ANSI

## (SDOs) activities; participation, and fees; ther government agencies; andards development.

# 2020 RFI Respondents

- 8 Committees

- 55 Standards

- Focus on microprocessors, design/verification, software, testing, smart manufacturing

- 1 Committee

- 3 Standards

- 4 Committees

- 10 Standards

ANSI

Focus on electronic packages, plastic chip carriers, supply chain traceability.

- 6 Committees

- 28 Standards

- devices

Focus on procurements, counterfeit parts, semiconductor devices

Focus on cyber, counterfeit, best manufacturing processes, and solid state

# **ANSI RFI 2022**

## Outreach

- 2020 RFI Respondents

- ANSI's networks of standards development organizations, technical experts and members

## **Respondent Organizations**

ANSI

Global Supply Chain Security for Microelectronics Standardization

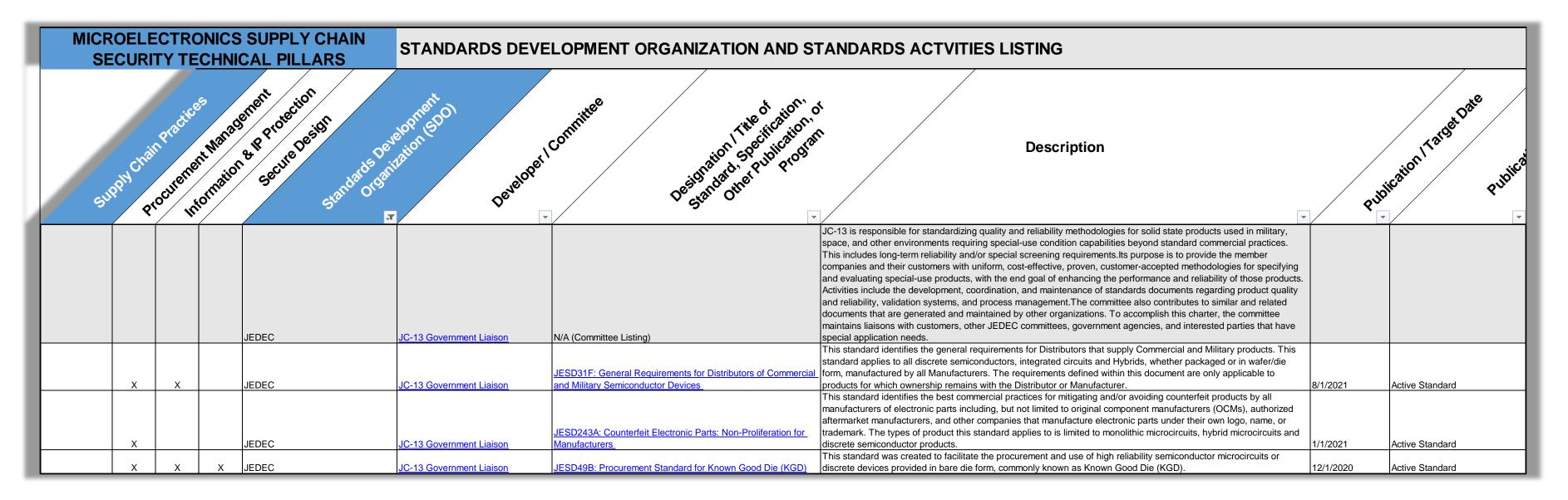

# **RFI Technical Pillars**

## **Evaluating Standards Content**

- Respondents were asked to identify which supply chain practice and risk management areas that their documents addressed.

- Standards may address more than one of the pillars.

- Discussions tomorrow are also organized by these pillars.

ANSI

|                                | Su                                         |

|--------------------------------|--------------------------------------------|

| Procurement<br>Management      | -<br>e<br>p<br>ti<br>a<br>a<br>c<br>N<br>v |

| Information & IP<br>Protection | -<br>a<br>c<br>fo<br>p                     |

| Secure Design                  | -<br>V<br>U<br>a<br>C                      |

## pply Chain Practices:

- Process and contractual considerations required for evaluating and defining engagements with external entities for procurements, including the risks/mitigations identified from the other supply chain practice areas. Procurement processes are focused on mitigating risks associated with sourcing IP and parts (e.g., counterfeit, DMSMS), and should include considerations for vendor demographics as identified in FY20 NDAA Section 224 (e.g., company ownership, location, workforce composition)

- Risks attributed to the confidentiality of intellectual property and information not intended for public dissemination. May overlap with other supply chain practice areas. Processes are focused on mitigations associated with networks and personnel.

- Design practices to improve assurance (e.g., verification and validation), manage risk when the part is outside vendor or user control, and address supply chain volatility (e.g., open architecture or modularity). May overlap with other supply chain practice areas.

# **Activity Listing & Pillar Affiliation**

## Contents:

**Pillars Affiliation Notation**: Individual standards are evaluated and note for their applicability to the pillars. This will assist to filter and identify existing and needed standards.

**Standards Listing**: Provides direct links to the committees, individual standards as well as brief context and status of documents to give users access to and a better understanding of what is available today.

\*Image not intended to be a full representation of all listing content

6

# **Overall Results**

- 16 Organizations

- Joint IEEE/ISO/IEC

- Joint SAE/ISO

- 31 Committees

- 113 Standards

operations operations configure integrity workforce workforce

## verification ap analysis fidentiality protection protection upply Chain counterfeit procurement mitigations

©2022

## **IEEE Committees**

- Design Automation Standards Committee (DASC) Microprocessor Standards Committee (MSC) Simulation Interoperability Standards Organization Standards Activity Committee (SISO SAC) Committee

- 1. 2. 3.

- 4. Smart Manufacturing Standards Committee (SM)

- Software and Systems Engineering Standards Committee (S2ESC) 5.

- Test Technology Standards Committee (TT) 6.

- IM/WM&A TC10 Waveform Generation Measurement and Analysis 7.

- 8. PES Substations Committee

## **Design Automation Standards Committee** (DASC)

| IEEE 2401-2019™, IEEE Standard Format for LSI- |  |

|------------------------------------------------|--|

| Package-Board Interoperable Design             |  |

Provides a method for specifying a common interoperable format for electronic systems design. The format provides a common way to specify information/data about the project management, netlists, components, design rules, and geometries used in the large-scale integration-package- board designs.

Establishes a format used to define the low-power design intent for electronic systems and electronic intellectual property (IP). The format provides the ability to specify the supply network, switches, isolation, retention, and other aspects relevant to power management of an electronic system. Specifies embeddable and encapsulating markup syntaxes for design intellectual property encryption and rights management, together with recommendations for integration with design specification formats described in IEEE 1800 (SystemVerilog) and IEEE 1076 (VHDL). Provides the definition of the language syntax and semantics for the IEEE 1800-2017 Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language, which is a unified hardware design, specification, and verification language. Describes a parameterized and abstracted power model enabling system, software, and hardware intellectual property (IP)-centric power analysis and optimization. It defines concepts for the development of parameterized, accurate, efficient, and complete power models for systems and hardware IP blocks usable for system

power analysis and optimization.

Defines a data format with which results of functional safety analyses (such as FMEA (Failure Mode and Effects Analysis), FMEDA (Failure Modes, Effects and Diagnostic Analysis), FMECA (Failure Mode, Effects and Criticality analysis), FTA (Fault Tree analysis) and related functional safety verification activities.

IEC 61523-4 Edition 1.0 2015-03 (IEEE 1801-2013™), IEEE/IEC International Standard - Design and Verification of Low-Power Integrated Circuits

IEEE P1735 - Recommended Practice for Encryption and Management of Electronic Design Intellectual Property (IP)

IEEE P1800 - Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language

IEEE P2416 - Standard for Power Modeling to Enable System-Level Analysis

IEEE P2851 - Standard for Functional Safety Data Format for Interoperability within the Dependability Lifecycle

ANSI

## **Microprocessor Standards** Committee (MSC)

## IEEE 1722.1-2021 - Standard for Device Discovery, **Connection Management, and Control Protocol for Time-**Sensitive Networking System:

Specifies the protocol, device discovery, connection management, and device control procedures used to facilitate interoperability between systems that use IEEE 802 time sensitive networking standards.

## IEEE 695-1990<sup>™</sup>, IEEE Standard for Microprocessor Universal Format for Object Modules:

Specifies the format of linkable, relocatable, and absolute object modules. MUFOM, the Microprocessor Universal Format for Object Modules, is designed to apply to a variety of target machines.

## **Smart Manufacturing** Standards Committee (SM)

# **Environments**:

IEEE P2879 - General Principles for Assessment of a **Smart Factory:** Defines basic terminologies, assessment process requirements, indicator metrics, assessment methods and assessment criteria of smart factories

detection deployment.

## **IEEE P2806 - System Architecture of Digital** <u>Representation for Physical Objects in Factory</u>

Defines the system architecture of digital representation for physical objects in factory environments. The system architecture describes the objective, important components, required data resources and basic establishing procedure of digital representation in factory environments.

## IEEE P2671 - Draft Standard for General Requirements of Online Detection Based on Machine Vision in

## Intelligent Manufacturing:

Specifies through the general requirements of online detection based on machine vision, including requirements for data format, data transmission processes, definition of application scenarios and performance metrics for evaluating the effect of online

## **Software and Systems Engineering Standards Committee (S2ESC)**

## **Test Technology Standards Committee (TT)**

## IEEE P1012 - Standard for System, Software, and Hardware Verification and Validation:

Addresses all system, software, and hardware life cycle processes including the Agreement, Organizational Project- Enabling, Project, Technical, Software Implementation, Software Support, and Software Reuse process groups.

### IEEE P1228 - Standard for Software Safety:

ANSI

Applies to software safety during the development, procurement, maintenance, and retirement of safety- critical software. Requires that software safety be considered within the context of the system safety program throughout the software lifecycle.

## IEEE 7002-2022 - Standard for Data Privacy Process:

Defines requirements for a systems/software engineering process for privacy-oriented considerations regarding products, services, and systems utilizing employee, customer or other external user's personal data. Extends across the life cycle from policy through development, quality assurance, and value realization.

## IEEE/ISO/IEC P41062 - Software Engineering - Life cycle processes -Software Acquisition:

Describes set of useful activities, tasks and methods that can be selected and applied during the acquisition of software or software services. Supply chain may include integration of commercial-off-theshelf (COTS), custom, or open source software.

# via this network.

Provides an interface between digital test generation tools and test equipment. A test description language is defined that: (a) facilitates the transfer of digital test vector data from CAE to ATE environments; (b) specifies pattern, format, and timing information sufficient to define the application of digital test vectors to a DUT; and (c) supports the volume of test vector data generated from structured tests.

IEEE 1687-2014<sup>™</sup>, IEEE Standard for Access and Control of Instrumentation Embedded within a Semiconductor Device: Describes a methodology for accessing instrumentation embedded within a semiconductor device, without defining the instruments or their features themselves, via the IEEE 1149.1<sup>™</sup> test access port (TAP) and/or other signals. The elements of the methodology include a hardware architecture for the on-chip network connecting the instruments to the chip pins, a hardware description language to describe this network, and a software language and protocol for communicating with the instruments

IEEE 1450-1999<sup>™</sup>, International Standard Test Interface Language (STIL) for Digital Test Vector Data:

## **IPC Committees & Standards**

| <u>2-19b Trusted Suppliers TG</u><br>(2-19 Supply Chain Traceability<br>& Trust Subcommittee) | <u>IPC-1791 B - Trusted Electronic Designer,</u><br><u>Manufacturer, and Assembler Requirements</u>                       | Provides minimum requirements<br>assembly organizations and/or<br>levels of confidence in the int<br>requirements to account for t                                    |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>B-10a Plastic Chip Carrier</u><br><u>Cracking TG</u>                                       | IPC/JEDEC-J-STD-033 D - Packaging and<br>Handling of Moisture Sensitive Non-Hermetic<br>Solid State Surface Mount Devices | Provides surface mount devic<br>packing, shipping and use of r<br>damage from moisture absorp<br>yield and reliability degradation<br>of 12 months from the seal date |

| <u>B-11a 3D Electronic Packages</u><br><u>Guideline TG</u>                                    | IPC-7091 - Design and Assembly Process<br>Implementation of 3D Components                                                 | Information to those who are<br>components or those who are<br>package may include multiple<br>package may also include seve<br>and some of which are integra         |

| <u>B-10a Plastic Chip Carrier</u><br><u>Cracking TG</u>                                       | IPC/JEDEC-J-STD-020 E - Moisture/Reflow<br>Sensitivity Classification of Plastic Surface<br>Mount Devices                 | Used to determine what mois<br>surface mount devices (SMDs<br>thermal and mechanical dama<br>operation. J-STD-020 covers c<br>lower temperature Sn-Pb asse            |

| <u>6-10d SMT Attachment</u><br><u>Reliability Test Methods TG</u>                             | IPC/JEDEC-9301 - Numerical Analysis<br>Guidelines for Microelectronics Packaging<br>Design and Reliability                | Basic tenets of a typical Finite<br>(and in some cases even expe<br>should be captured and provi                                                                      |

| <u>6-10d SMT Attachment</u><br>Reliability Test Methods TG                                    | IPC-1782 A - Standard for Manufacturing and<br>Supply Chain Traceability of Electronic<br>Products                        | Minimum requirements for m<br>1782A applies to all products,<br>used in the manufacture of pr                                                                         |

ANSI

nents, policies and procedures for printed board design, fabrication, and /or companies to become trusted sources for markets requiring high ntegrity of delivered products. IPC-1791B expands the standard's r trusted sources of cable and wire harness assemblies.

rice manufacturers and users with standardized methods for handling, f moisture/reflow sensitive components. These methods help avoid prption and exposure to solder reflow temperatures that can result in tion and damaged components. Procedures provide a minimum shelf life date when properly implemented. Developed by IPC and JEDEC.

re designing, developing or using 3D-packaged semiconductor are considering 3D package implementation. The 3D semiconductor ole die elements—some homogeneous and some heterogeneous. The everal discrete passive SMT devices, some of which are surface mounted grated (embedded) within the components' substrate structure.

Disture-sensitivity-level (MSL) classification level should be used so that Ds) can be properly packaged, stored and handled to avoid subsequent mage during the assembly solder reflow attachment and/or repair s components to be processed at higher temperatures for lead-free and ssemblies.

te Element Analysis (FEA) model, as well as, to educate new designers perienced designers) on the basic information and best practices that vided to technical reviewers of the results of FEA data.

manufacturing and supply chain traceability based on perceived risk. IPCts, processes, assemblies, parts, components, equipment and other items printed board assemblies and in mechanical assembly

# JEDEC Committees

<u>JC-13 Government</u> <u>Liaison</u> JESD31F: General Requirements for Distributors of Commercial and Military Semiconductor Devices

Identifies the general requirements for Distributors that supply Commercial and Military products. This standard applies to all discrete semiconductors, integrated circuits and Hybrids, whether packaged or in wafer/die form, manufactured by all Manufacturers. The requirements defined within this document are only applicable to products for which ownership remains with the Distributor or Manufacturer.

<u>JC-13 Government</u> <u>Liaison</u> JESD243A: Counterfeit Electronic Parts: Non-Proliferation for Manufacturers Identifies the best commercial practices for mitigating and/or avoiding counterfeit products by all manufacturers of electronic parts including, but not limited to original component manufacturers (OCMs), authorized aftermarket manufacturers, and other companies that manufacture electronic parts under their own logo, name, or trademark. The types of product this standard applies to is limited to monolithic microcircuits, hybrid microcircuits and discrete semiconductor products.

<u>JC-13 Government</u> <u>Liaison</u>

ANSI

JESD49B: Procurement Standard for Known Good Die (KGD)

Facilitates the procurement and use of high reliability semiconductor microcircuits or discrete devices provided in bare die form, commonly known as Known Good Die (KGD).

JC-13 is responsible for standardizing quality and reliability methodologies for solid state products used in military, space, and other environments requiring special-use condition capabilities beyond standard commercial practices. This includes long-term reliability and/or special screening requirements. Its purpose is to provide the member companies and their customers with uniform, cost-effective, proven, customer-accepted methodologies for specifying and evaluating special-use products, with the end goal of enhancing the performance and reliability of those products.

## **SAE International Committees**

- CE-12 Solid State Devices 1.

- G-14 Americas Aerospace Quality 2.

- G-19 Counterfeit Electronics Avoidance and Detection 3.

- 4. G-23 Manufacturing Management

- G-32 Cyber Physical Systems 5.

- Avionics Process Management Committee (APMC) 6.

- TEVEES18A Vehicle Cybersecurity Systems Engineering Committee 7.

- 8. Vehicle Cybersecurity Systems Engineering Committee

©2022 14

## G-19A Test Laboratory Standards Development Committee

|            | 5171A - Test Methods Standard; General Requirements,<br>pect/Counterfeit, Electrical, Electronic, and Electromechanical<br>ts.                                                 | <u>AS6171/7 - Techn</u><br><u>Detection by Elec</u>                           |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| <u>AS6</u> | 5171/1 - Suspect/Counterfeit Test Evaluation Method                                                                                                                            | AS6171/8 - Techn<br>Detection by Ram                                          |

| by E       | 5171/2A - Techniques for Suspect/Counterfeit EEE Parts Detection<br>External Visual Inspection, Remarking and Resurfacing, and Surface<br>ture Analysis Using SEM Test Methods | <u>AS6171/9 - Techn</u><br><u>Detection by Fou</u><br><u>Methods</u>          |

|            | 5171/3 - Techniques for Suspect/Counterfeit EEE Parts Detection<br>K-ray Fluorescence Test Methods                                                                             | AS6171/10 - Tech<br>Detection by The                                          |

|            | 5171/4 - Techniques for Suspect/Counterfeit EEE Parts Detection<br>Delid/Decapsulation Physical Analysis Test Methods                                                          | AS6171/11 - Tech<br>Detection by Des                                          |

|            | 5171/5 - Techniques for Suspect/Counterfeit EEE Parts Detection<br>Radiological Test Methods                                                                                   | AS6810 - Require<br>Test Laboratories<br>Accordance with<br>Associated Test N |

|            | 5171/6 - Techniques for Suspect/Counterfeit EEE Parts Detection<br>Acoustic Microscopy (AM) Test Methods                                                                       | <u>SA</u>                                                                     |

ANSI

nniques for Suspect/Counterfeit EEE Parts ectrical Test Methods

nniques for Suspect/Counterfeit EEE Parts man Spectroscopy Test Methods

nniques for Suspect/Counterfeit EEE Parts ourier Transform Infrared Spectroscopy (FTIR) Test

<u>chniques for Suspect/Counterfeit EEE Parts</u> <u>ermogravimetric Analysis (TGA) Test Methods</u>

<u>chniques for Suspect/Counterfeit EEE Parts</u> esign Recovery Test Methods

rements for Accreditation Bodies when Accrediting es Performing Detection of Suspect/Counterfeit in h AS6171 General Requirements and the <u>Methods</u>

AE Counterfeit Defect Coverage Tool

©2022

15

## **G-32 Cyber Physical Systems**

## JA7496 - Cyber Physical Systems Security Engineering Plan (CPSSEP)

Supports developing a systems engineering approach to standardization of cyber physical systems security.

### JA6801 - Cyber Physical Systems Security Hardware Assurance:

- (a) assess and address weaknesses and vulnerabilities of cyber physical system hardware utilizing systems engineering principles to ensure security and resilience throughout the lifecycle of the system,

- (b) conduct EEE component level assurance and analysis, considering impact on the hardware, software, and firmware, in the product or system,

- (c) Address concerns including interfaces and network of the system and command and control that could be manipulated through a physical process and/or physical input of the data.

## JA6678 – Cyber Physical Systems Security Software Assurance:

- (a) assess and address vulnerabilities of cyber physical system software utilizing systems engineering principles to ensure security and resilience throughout the lifecycle of the system,

- (b) conduct software assurance and analysis, considering impact on the product's software, hardware, and firmware,

- (c) Address concerns including consideration of the interfaces and network of the system and command and control that could be manipulated through a physical process and/or physical input of the data flow and computation,

- (d) perform design validation and verification to assess security and resiliency of software impacting the cyber physical system safety, security and integrity across the complete lifecycle.

## **Avionics Process Management Committee (APMC)**

**EIA933C - Requirements for a COTS Assembly Management Plan:** This document applies to the development of Plans for integrating and managing COTS assemblies in electronic equipment and Systems for the commercial, military, and space markets; as well as other ADHP markets that wish to use this document.

Requirements for developing a DMSMS Management Plan to assure customers that the Plan owner is using a proactive DMSMS process for minimizing the cost and impact that part and material obsolescence will have on equipment delivered by the Plan owner. Owners of DMSMS Management Plans include System Integrators, Original Equipment Manufacturers (OEM), and logistics support providers. Technical requirements ensure that the Plan owner can meet the requirement of having a process to address obsolescence as required by DoD Programs as required by MIL-STD-3018 "Parts Management".

## **EIASTD4899C - Requirements for an Electronic Components** Management Plan:

Development of Plans for integrating and managing electronic components in equipment for the military and commercial aerospace markets. Examples of electronic components, as described in this document, include resistors, capacitors, diodes, integrated circuits, hybrids, application specific integrated circuits, wound components, and relays.

STD0016A Standard for Preparing a DMSMS Management Plan:

©2022

16

186

# **SAE International Key Standards**

| <u>G-14 Americas Aerospace</u><br><u>Quality</u> | <u>AS9100D - Quality Management Systems -</u><br><u>Requirements for Aviation, Space, and</u><br><u>Defense Organizations</u> | Includes ISO 9001:2<br>additional aviation,<br>notes.                                                            |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| CE-12 Solid State Devices                        | AS6294/2 Requirements for Plastic<br>Encapsulated Microcircuits in Military and<br>Avionics Applications.                     | Establishes commor<br>Plastic Encapsulated<br>environments. This<br>PEM construction an<br>the supply chain site |

AS6294/4 Requirements for Plastic **Encapsulated Semiconductor Devices in** Military and Avionics Applications.

Establishes common industry practices, and screening and qualification testing, of plastic encapsulated discrete semiconductors (PEDs) for use in military and avionics application environments. Addresses many of the concerns associated with PED construction and manufacturing, primarily the non-hermetic packaging and the supply chain situation of multiple material sets and assembly sites.

| <u>G-19 Counterfeit</u>   | AS5553D - Counterfeit Electrical, Electronic, |

|---------------------------|-----------------------------------------------|

|                           | and Electromechanical (EEE) Parts;            |

| Electronics Avoluance and | Avoidance, Detection, Mitigation, and         |

| <u>Detection</u>          | Disposition.                                  |

For use by organizations that procure and/or integrate and/or repair EEE parts and/or assemblies containing such items, including maintenance, repair, and overhaul (MRO) organizations and can be flowed down supply chains through contract to ensure reliability and robustness. It was revised to take into account DFARS 252.246-7008 – Sources of Electronic Parts, to deal with traceability and control throughout the supply chain.

:2015 quality management system requirements and specifies n, space, and defense industry requirements, definitions, and

on industry practices, and screening and qualification testing, of ed Microcircuits (PEMs) for use in military and avionics application is document addresses many of the concerns associated with and manufacturing, primarily the non-hermetic packaging and ituation of multiple material sets and assembly sites.

# The Open Group

**Open Trusted Technology Forum**  Open Trusted Technology Provider<sup>™</sup> Standard (O-TTPS); Technically equivalent to ISO/IEC 20243

- ٠

The Open Trusted Technology Forum provides a collaborative environment to facilitate creating international standards focused on supply chain security to establish a unified view of practicing supply chain risk management (SCRM) for information and communication technology (ICT) products.

OTTF has developed two preeminent international certification programs:

- The Open Trusted Technology Provider <sup>™</sup> Standard (O-TTPS) Certification Program •

- Certified Trusted Technology Practitioner (Open CTTP) Professional Certification. •

• Set of guidelines, recommendations and requirements that help assure against maliciously tainted and counterfeit products throughout commercial off-the-shelf (COTS) information and communication technology (ICT) product lifecycles. All phases of a product's life cycle: design, sourcing, build,

fulfillment, distribution, sustainment, and disposal

Focuses on verification of the procedures used within the organization to maintain security and integrity of the supply chain,

# **Telecommunications Industry Association** (TIA)

**TIA QUEST** Forum's Supply Chain Security Working Group

SCS 9001: Global Supply Chain Security Standard (Handbook)

SCS 9001 addresses the urgent need for an information and communications technology (ICT) specific standard for global supply chain security. The standard provides guidance for key components of supply chain security: (1) Secure software development; (2) Validation methods for ensuring software ID and source traceability; (3) Product security; (4) Governmental requirements on source of origin and transparency of internal controls.

TIA QUEST Forum Working Groups collaboratively identify best practices and execute key projects and initiatives to address a range of global ICT issues. The Supply Chain Security working group:

- Worked over 24 months to get the document prepared •

- SCS 9001 is a process-based standard, built on top of a quality management system (QMS) •

- The internal SCS 9001 comment review has been completed with the Integrated Global Quality (IGQ) Working Group •

- The document was out for comment review to other specific industry subject matter exerts •

- The deadline for all comment inputs was: 26 October 2021 •

- Comment reviews took place in November •

ANSI

- SCS 9001 Pilot Auditor Training has been conducted with 25 global AB and CB auditors participating •

- SCS 9001 pilots are taking place in November and December 2021. Let us know if you're interested in participating.

- SCS 9001 R1.0 is expected to be sent for a full TIQ QuEST Forum vote in December 2021 •

# **Other Activities Identified**

- Accellera

- Alliance for Telecommunications Industry Solutions (ATIS)

- National Institute of Standards and Technology (NIST)

- Open Compute Project (OCP)

- RISC-V International

- Silicon Integration Initiative (Si2)

- Transported Asset Protection Association (TAPA)

- Unified Extensible Firmware Interface Forum (UEFI)

\*Require SME evaluation for applicability

## Takeaways

- Several standards organizations are developing related standards.

- Collectively, there is a toolbox industry and government can leverage.

- No commonly agreed upon high-level specification/practice providing how to leverage the collection of existing resources.

- Several forums are well-positioned to fill gaps and support future standards development needs.

- Workshop discussions will likely identify other useful documents.

- Other organizations wishing to submit their documents should utilize the excel and submit to <u>cbernat@ansi.org</u> and <u>jmccabe@ansi.org</u>

# **ANSI Staff Contacts**

Jim McCabe Senior Director, Standards Facilitation 1-212-642-8921; jmccabe@ansi.org

www.ansi.org

**Christine D. Bernat**

Associate Director, Standards Facilitation 1-212-642-8919 <u>cbernat@ansi.org</u>

www.ansi.org